# Keysight U7233A DDR1 Compliance Test Application

Compliance Testing Notes

## **Notices**

© Keysight Technologies 2007-2008, 2015

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

## Manual Part Number u7233-97002

### **Edition**

Fourth Edition, October 2015

Printed in Malaysia

Keysight Technologies. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

## Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE. IN FUTURE EDITIONS. FURTHER. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW. KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN. INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN, SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

## **Technology Licenses**

The hard ware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

## Restricted Rights Legend

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Keysight Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR

52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

### Safety Notices

### CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

## WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

Quick Reference **Table 1** Cycles and Signals

NOTE: 1 = Single Ended probing; 2 = Differential probing; 3 = 2 x Single Ended probing

| TEST             | T Cycle |           |           | Based on Test Definition |           |           |           |                      | Required to Perform on Scope |            |            |            |            |                      | Opt.     |

|------------------|---------|-----------|-----------|--------------------------|-----------|-----------|-----------|----------------------|------------------------------|------------|------------|------------|------------|----------------------|----------|

|                  | Read    | Write     | DQ        | DQS                      | CK        | ADD       | Ctrl      | Data<br>Mask<br>Ctrl | DQ                           | DQS        | СК         | ADD        | Ctrl       | Data<br>Mask<br>Ctrl | CS#      |

| SlewR            |         | $\sqrt{}$ | $\sqrt{}$ |                          | $\sqrt{}$ |           | $\sqrt{}$ | $\sqrt{}$            | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$           |          |

| SlewF            |         | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$                | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$            | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$           |          |

| VIH(ac)          |         | V         | V         | V                        |           |           | $\sqrt{}$ | <b>V</b>             | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$           |          |

| VIH(dc)          |         | $\sqrt{}$ | V         |                          | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$            | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$           |          |

| VIL(ac)          |         | V         | V         | V                        |           |           | $\sqrt{}$ | <b>V</b>             | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$           |          |

| VIL(dc)          |         | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$                | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$            | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$           |          |

| VOH(ac)          |         | V         |           | V                        |           | V         |           | $\sqrt{}$            | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$           |          |

| VOL(ac)          |         | $\sqrt{}$ | <b>V</b>  | V                        | V         | $\sqrt{}$ | V         |                      | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ |                      |          |

| AC<br>Overshoot  |         | $\sqrt{}$ | 1         | √                        | 1         | √         | √         | V                    | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$           |          |

| AC<br>Undershoot |         | $\sqrt{}$ | V         | √                        | $\sqrt{}$ | √         | √         | V                    | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$           |          |

| VID(ac)          |         | V         |           | V                        | <b>V</b>  |           |           |                      |                              | $\sqrt{3}$ | $\sqrt{3}$ |            |            |                      |          |

| VIX(ac)          |         | $\sqrt{}$ |           |                          | $\sqrt{}$ |           |           |                      |                              | $\sqrt{3}$ | $\sqrt{3}$ |            |            |                      |          |

| tAC              | √       |           | <b>V</b>  |                          | <b>V</b>  |           |           |                      | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | √        |

| tDQSCK           | √       |           |           |                          | $\sqrt{}$ |           |           |                      | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | <b>√</b> |

| tCK(avg)         |         |           |           |                          |           |           |           |                      |                              |            | $\sqrt{2}$ |            |            |                      |          |

| tCH(avg)         |         |           |           |                          | V         |           |           |                      |                              |            | $\sqrt{2}$ |            |            |                      |          |

| tCL(avg)         |         |           |           |                          |           |           |           |                      |                              |            | $\sqrt{2}$ |            |            |                      |          |

| tHZ(DQ)          | √       |           | <b>V</b>  |                          | V         |           |           |                      | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | √        |

| tHZ(DQS)         | √       |           |           | <b>V</b>                 | <b>V</b>  |           |           |                      | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | √        |

| tLZ(DQS)         | √       |           |           | $\sqrt{}$                | $\sqrt{}$ |           |           |                      | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | √        |

| tLZ(DQ)          | √       |           | <b>V</b>  |                          | <b>V</b>  |           |           |                      | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | √        |

| tDQSQ            | √       |           | <b>V</b>  | <b>V</b>                 |           |           |           |                      | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | √        |

| tQH              | √       |           | <b>V</b>  | <b>√</b>                 |           |           |           |                      | $\sqrt{2}$                   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | √        |

| TEST             | Су      | cle       |           | Base                     | d on      | Test De   | efinitio  | n                    | R                            | equire     | d to F     | erform     | on Sc      | ope                  | Opt.     |

Table 1

Cycles and Signals

NOTE: 1 = Single Ended probing; 2 = Differential probing; 3 = 2 x Single Ended probing

|                       | Read     | Write     | DQ       | DQS       | СК        | ADD       | Ctrl      | Data<br>Mask<br>Ctrl | DQ           | DQS        | CK         | ADD        | Ctrl       | Data<br>Mask<br>Ctrl | CS#      |

|-----------------------|----------|-----------|----------|-----------|-----------|-----------|-----------|----------------------|--------------|------------|------------|------------|------------|----------------------|----------|

| tDQSS                 |          | $\sqrt{}$ |          | $\sqrt{}$ | $\sqrt{}$ |           |           |                      | $\sqrt{2}$   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | √        |

| tDQSH                 | V        |           |          | V         |           |           |           |                      | $\sqrt{2}$   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | <b>V</b> |

| tDQSL                 | <b>V</b> |           |          | $\sqrt{}$ |           |           |           |                      | $\sqrt{2}$   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | <b>√</b> |

| tDSS                  |          | $\sqrt{}$ |          | V         | $\sqrt{}$ |           |           |                      | $\sqrt{2}$   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | <b>V</b> |

| tDSH                  |          | $\sqrt{}$ |          | $\sqrt{}$ | $\sqrt{}$ |           |           |                      | $\sqrt{2}$   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | <b>V</b> |

| tWPST                 |          | $\sqrt{}$ |          | V         |           |           |           |                      | $\sqrt{2}$   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | <b>V</b> |

| tWPRE                 |          | $\sqrt{}$ |          | V         |           |           |           |                      | $\sqrt{2}$   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | <b>V</b> |

| tRPRE                 | V        |           |          | V         |           |           |           |                      | $\sqrt{2}$   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | <b>V</b> |

| tRPST                 | V        |           |          | $\sqrt{}$ |           |           |           |                      | $\sqrt{2}$   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | √        |

| tDS(base)             |          | $\sqrt{}$ | <b>V</b> |           |           |           |           |                      | $\sqrt{2}$   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | <b>√</b> |

| tDH(base)             |          | $\sqrt{}$ | V        |           |           |           |           |                      | $\sqrt{2}$   | $\sqrt{2}$ | $\sqrt{2}$ |            |            |                      | <b>V</b> |

| tIS(base)             | V        |           |          |           | $\sqrt{}$ | $\sqrt{}$ | V         |                      |              |            | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ |                      | <b>V</b> |

| tIH(base)             | V        |           |          |           | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ |                      |              |            | $\sqrt{2}$ | $\sqrt{2}$ | $\sqrt{2}$ |                      | <b>V</b> |

| High State<br>Ringing |          |           | 1        | V         |           | √         | V         | $\sqrt{}$            | √1,2         | √1,2       |            | √1,2       | √1,2       | $\sqrt{1,2}$         |          |

| Low State<br>Ringing  |          |           | 1        | $\sqrt{}$ |           | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$            | $\sqrt{1,2}$ | √1,2       |            | √1,2       | √1,2       | $\sqrt{1,2}$         |          |

| tJIT(per)             |          |           |          |           | <b>√</b>  |           |           |                      |              |            | $\sqrt{2}$ |            |            |                      |          |

| tJIT(cc)              |          |           |          |           | $\sqrt{}$ |           |           |                      |              |            | $\sqrt{2}$ |            |            |                      |          |

| tERR(nper)            |          |           |          |           | <b>√</b>  |           |           |                      |              |            | $\sqrt{2}$ |            |            |                      |          |

| tJIT(duty)            |          |           |          |           | V         |           |           |                      |              |            | $\sqrt{2}$ |            |            |                      |          |

## DDR1 Compliance Test Application - At A Glance

The Keysight U7233A DDR1 Compliance Test Application is a DDR (Double Data Rate) test solution that covers electrical, clock and timing parameters of the JEDEC (Joint Electronic Device Engineering Council) specifications, specifically *JESD79E*. The software helps you in testing all the un-buffered device under test (DUT) compliance, with the Keysight 54850A, 8000 and 80000 and 90000A series Infiniium digital storage oscilloscope.

There are 2 main categories of test modes:

- Compliance Tests These tests are based on the DDR JEDEC compliance specifications and are compared to corresponding compliance test limits.

- Debug Mode These tests are not based on any compliance specification. The primary use of these tests is to perform signal debugging.

The DDR1 Compliance Test Application:

- · Lets you select individual or multiple tests to run.

- · Lets you identify the device being tested and its configuration.

- · Shows you how to make oscilloscope connections to the device under test.

- · Automatically checks for proper oscilloscope configuration.

- Automatically sets up the oscilloscope for each test.

- · Allows you to determine the number of trials for each test, with the new multi trial run capability.

- Provides detailed information of each test that has been run. The result of maximum twenty five worst trials can be displayed at any one time.

- Creates a printable HTML report of the tests that have been run.

The minimum number of probes required for the tests are:

- · Clock tests 1 probe.

- Electrical tests 3 probes.

- Clock Timing tests 3 probes.

- · Advanced Debug tests 3 probes.

### NOTE

The tests performed by the DDR1 Compliance Test Application are intended to provide a quick check of the physical layer performance of the DUT. These tests are not replacement for an exhaustive test validation plan.

DDR SDRAM electrical, clock and timing test standards and specifications are described in the *JESD79E* document. For more information, please refer to JEDEC web site at www.jedec.org.

### Required Equipment and Software

In order to run the DDR1 automated tests, you need the following equipment and software:

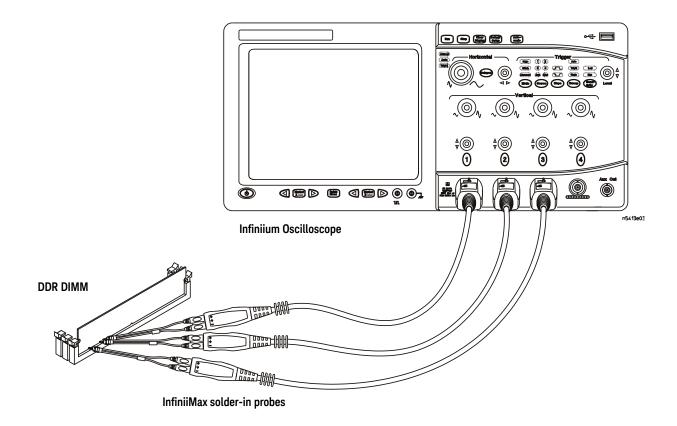

- 54850A, 8000, 80000 or 90000A series Infiniium Digital Storage Oscilloscope. Keysight recommends using 4 GHz and higher bandwidth oscilloscope.

- Infiniium software revision 05.30 or later (54850A, 8000 and 80000 series Infiniium Digital Storage Oscilloscope) OR

- Baseline software revision 1.0 (90000A series Infiniium Digital Storage Oscilloscope).

- · U7233A DDR1 Compliance Test Application, version 1.20 and higher.

- · RAM reliability test software.

- 1169A, 1168A, 1134A, 1132A or 1131A InfiniiMax probe amplifiers.

- N5381A or E2677A differential solder-in probe head, N5382A or E2675A differential browser probe head, N5425A ZIF probe head or N5426A ZIF tips.

- Any computer motherboard system that supports memory.

- Keyboard, gty = 1, (provided with the Keysight Infiniium oscilloscope).

- Mouse, qty = 1, (provided with the Keysight Infiniium oscilloscope).

### Below are the required licenses:

- U7233A DDR1 Compliance Test Application license.

- N5414A InfiniiScan software license (for 90000A, 80000 and 54850A series).

- · N5415A InfiniiScan software license (for 8000 series).

- · N5404A Deep memory option (optional).

### In This Book

This manual describes the tests that are performed by the DDR1 Compliance Test Application in more detail; it contains information from (and refers to) the *JESD79E*, and it describes how the tests are performed.

- Chapter 1, "Installing the DDR1 Compliance Test Application shows how to install and license the automated test application software (if it was purchased separately).

- Chapter 2, "Preparing to Take Measurements shows how to start the DDR1 Compliance Test Application and gives a brief overview of how it is used.

- Chapter 3, "Single-Ended Signals AC Input Parameters Tests shows how to run the single-ended signals AC input parameters tests. This chapter includes maximum ac output logic high and minimum ac output logic low.

- Chapter 4, "Single-Ended Signals AC Output Parameters Tests shows how to run the single-ended signals AC output parameters tests. This chapter includes input logic high tests, input logic low tests, and maximum and minimum ac output logic high and low.

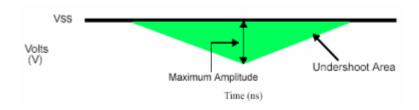

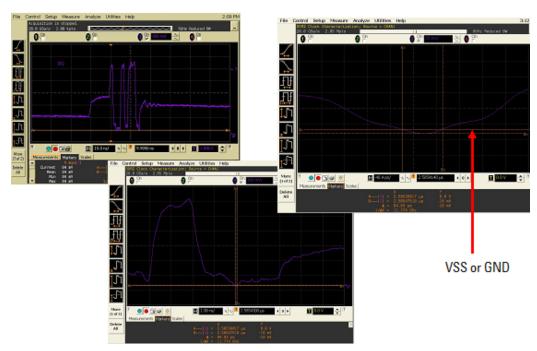

- Chapter 5, "Single-Ended Signals Overshoot/Undershoot Tests describes the AC overshoot and undershoot tests probing and method of implementation.

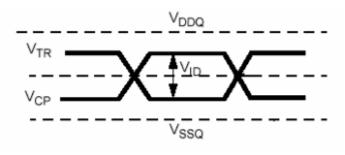

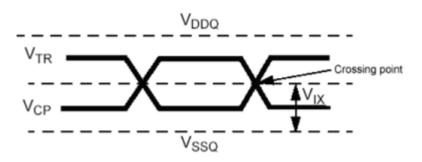

- Chapter 6, "Differential Signals AC Input Parameters Tests describes the V<sub>ID</sub> AC differential input voltage tests and V<sub>IX</sub> AC differential cross point voltage tests.

- Chapter 8, "Clock Timing (CT) Tests describes the clock timing operating conditions of SDRAM as

defined in the specification.

- Chapter 7, "Data Strobe Timing (DST) Tests describes various data strobe timing tests including tHZ(DQ), tHZ(DQS), tLZ(DQS), tLZ(DQ), tDQSQ, tQH, tDQSS, tDQSH, tDQSL, tDSS, tDSH, tWPST, tWPRE, tRPRE and tRPST tests.

- Chapter 9, "Data Mask Timing (DMT) Tests describes the DQ and DM input setup time and input hold time.

- Chapter 10, "Command and Address Timing (CAT) Tests describes the address and control input setup time and input hold time.

- Chapter 11, "Advanced Debug Mode Clock Tests describes the measurement clock tests including clock period jitter, cycle to cycle period jitter, cumulative error, and half period jitter.

- Chapter 12, "Advanced Debug Mode High-Low State Ringing Tests shows the high state and low state ringing test method of implementation.

- Chapter 13, "Calibrating the Infiniium Oscilloscope and Probe describes how to calibrate the

oscilloscope in preparation for running the automated tests.

- Chapter 14, "InfiniiMax Probing describes the probe amplifier and probe head recommendations for testing.

- Chapter 15, "Common Error Messages describes the error dialog boxes that can appear and how to remedy the problem.

### See Also

- The DDR1 Compliance Test Application's online help, which describes:

- Starting the DDR1 compliance test application.

- · Creating or opening a test project.

- Setting up DDR1 test environment.

- · Selecting tests.

- Configuring selected tests.

- · Connecting the oscilloscope to the DUT.

- Running tests.

- · Viewing test results.

- · Viewing/printing the HTML test report.

- Understanding the HTML report.

- Saving test projects.

# Contact Keysight

For more information on DDR1 Compliance Test Application or other Keysight Technologies' products, applications and services, please contact your local Keysight office. The complete list is available at:

Korea:

### www.keysight.com/find/contactus

### Phone or Fax

United States: (tel) 800 829 4444

(fax) (81) 426 56 7840

(tel) 800 829 4444 (tel) (080) 769 0800 (fax) 800 829 4433 (fax) (080) 769 0900

Canada: Latin America:

(tel) 877 894 4414 (tel) (305) 269 7500

(fax) 800 746 4866 Taiwan:

China: (tel) 0800 047 866

(tel) 800 810 0189 (fax) 0800 286 331

(fax) 800 820 2816 Other Asia Pacific Countries:

Europe: (tel) (65) 6375 8100 (tel) 31 20 547 2111 (fax) (65) 6755 0042

Japan: E-mail: tm\_ap@keysight.com

(tel) (81) 426 56 7832

# Contents

|   | Quick Reference 3                                                                                                                                      |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | DDR1 Compliance Test Application — At A Glance 5                                                                                                       |

|   | Required Equipment and Software 6                                                                                                                      |

|   | In This Book 7                                                                                                                                         |

|   | See Also 8                                                                                                                                             |

|   | Contact Keysight 9                                                                                                                                     |

|   | Phone or Fax 9                                                                                                                                         |

| 1 | Installing the DDR1 Compliance Test Application                                                                                                        |

|   | Installing the Software 22                                                                                                                             |

|   | Installing the License Key 23                                                                                                                          |

| 2 | Preparing to Take Measurements                                                                                                                         |

|   | Calibrating the Oscilloscope 26                                                                                                                        |

|   | Starting the DDR1 Compliance Test Application 27 Online Help Topics 29                                                                                 |

| 3 | Single-Ended Signals AC Input Parameters Tests                                                                                                         |

|   | Probing for Single-Ended Signals AC Input Parameters Tests 32  Test Procedure 32                                                                       |

|   | SlewR Test Method of Implementation 35                                                                                                                 |

|   | Signals of Interest 36  Test Definition Notes from the Specification 36  PASS Condition 36  Measurement Algorithm 36  Test References 37               |

|   | SlewF Test Method of Implementation 38                                                                                                                 |

|   | Signals of Interest 39  Test Definition Notes from the Specification 39  PASS ConditionPASS Condition 39  Measurement Algorithm 39  Test References 40 |

| Signals of Interest 41 Test Definition Notes from the Specification 42 PASS Condition 42 Measurement Algorithm 42 Test References 43  VIH(DC) Test Method of Implementation 44 Signals of Interest 44 Test Definition Notes from the Specification 45 PASS Condition 45 Measurement Algorithm 45 Test References 46  VIL(AC) Test Method of Implementation 47 Signals of Interest 47 Test Definition Notes from the Specification 48 PASS Condition 48 Measurement Algorithm 48 Test References 49  VIL(DC) Test Method of Implementation 50 Signals of Interest 50 Test Definition Notes from the Specification 51 PASS Condition 51 Measurement Algorithm 51 Test References 51  4 Single-Ended Signals AC Output Parameters Tests |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Measurement Algorithm 42 Test References 43  VIH(DC) Test Method of Implementation 44 Signals of Interest 44 Test Definition Notes from the Specification 45 PASS Condition 45 Measurement Algorithm 45 Test References 46  VIL(AC) Test Method of Implementation 47 Signals of Interest 47 Test Definition Notes from the Specification 48 PASS Condition 48 Measurement Algorithm 48 Test References 49  VIL(DC) Test Method of Implementation 50 Signals of Interest 50 Test Definition Notes from the Specification 51 PASS Condition 51 Measurement Algorithm 51 Test References 51                                                                                                                                             |    |

| Signals of Interest 44  Test Definition Notes from the Specification 45  PASS Condition 45  Measurement Algorithm 45  Test References 46  VIL(AC) Test Method of Implementation 47  Signals of Interest 47  Test Definition Notes from the Specification 48  PASS Condition 48  Measurement Algorithm 48  Test References 49  VIL(DC) Test Method of Implementation 50  Signals of Interest 50  Test Definition Notes from the Specification 51  PASS Condition 51  Measurement Algorithm 51  Test References 51  4 Single-Ended Signals AC Output Parameters Tests                                                                                                                                                                  |    |

| Test Definition Notes from the Specification 45 PASS Condition 45 Measurement Algorithm 45 Test References 46  VIL(AC) Test Method of Implementation 47 Signals of Interest 47 Test Definition Notes from the Specification 48 PASS Condition 48 Measurement Algorithm 48 Test References 49  VIL(DC) Test Method of Implementation 50 Signals of Interest 50 Test Definition Notes from the Specification 51 PASS Condition 51 Measurement Algorithm 51 Test References 51                                                                                                                                                                                                                                                          |    |

| Signals of Interest 47 Test Definition Notes from the Specification 48 PASS Condition 48 Measurement Algorithm 48 Test References 49  VIL(DC) Test Method of Implementation 50 Signals of Interest 50 Test Definition Notes from the Specification 51 PASS Condition 51 Measurement Algorithm 51 Test References 51  4 Single-Ended Signals AC Output Parameters Tests                                                                                                                                                                                                                                                                                                                                                               |    |

| Test Definition Notes from the Specification 48 PASS Condition 48 Measurement Algorithm 48 Test References 49  VIL(DC) Test Method of Implementation 50 Signals of Interest 50 Test Definition Notes from the Specification 51 PASS Condition 51 Measurement Algorithm 51 Test References 51  4 Single-Ended Signals AC Output Parameters Tests                                                                                                                                                                                                                                                                                                                                                                                      |    |

| VIL(DC) Test Method of Implementation 50 Signals of Interest 50 Test Definition Notes from the Specification 51 PASS Condition 51 Measurement Algorithm 51 Test References 51  4 Single-Ended Signals AC Output Parameters Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| Signals of Interest 50  Test Definition Notes from the Specification 51  PASS Condition 51  Measurement Algorithm 51  Test References 51  4 Single-Ended Signals AC Output Parameters Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| Ducking for Cinals Ended Cinasts AC Cutaut Description Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| Probing for Single-Ended Signals AC Output Parameters Tests  Test Procedure 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54 |

| VOH(AC) Test Method of Implementation 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| Signals of Interest 57  Test Definition Notes from the Specification 58  PASS Condition 58  Measurement Algorithm 58  Test References 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| VOL(AC) Test Method of Implementation 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| Signals of Interest 59  Test Definition Notes from the Specification 60  PASS Condition 60  Measurement Algorithm 60  Test References 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 5 Single-E  | Ended Signals Overshoot/Undershoot Tests                                                                                                                                                                         |    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|             | Probing for Overshoot/Undershoot Tests 62                                                                                                                                                                        |    |

|             | Test Procedure 62                                                                                                                                                                                                |    |

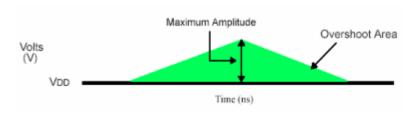

|             | AC Overshoot Test Method of Implementation 65                                                                                                                                                                    |    |

|             | Signals of Interest 65 Test Definition Notes from the Specification 66 PASS Condition 66 Measurement Algorithm 66 Test References 67                                                                             |    |

|             | AC Undershoot Test Method of Implementation 68                                                                                                                                                                   |    |

|             | Signals of Interest 68  Test Definition Notes from the Specification 69  PASS Condition 69  Measurement Algorithm 69  Test References 70                                                                         |    |

| 6 Different | tial Signals AC Input Parameters Tests                                                                                                                                                                           |    |

|             | Probing for Differential Signals AC Input Parameters Tests 72  Test Procedure 72                                                                                                                                 |    |

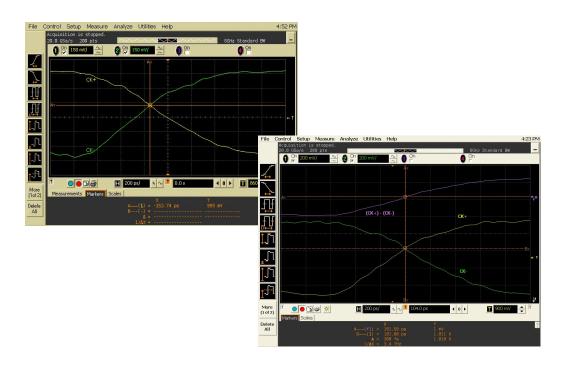

|             | VID(AC), AC Differential Input Voltage - Test Method of Implementation  Signals of Interest 76  Test Definition Notes from the Specification 77  PASS Condition 77  Measurement Algorithm 77  Test References 77 |    |

|             | VIX(AC), AC Differential Input Cross Point Voltage -Test Method of Implementation Signals of Interest 79 PASS Condition 79 Measurement Algorithm 79 Test References 79                                           | 78 |

| 7 Data Str  | robe Timing (DST) Tests                                                                                                                                                                                          |    |

|             | Probing for Data Strobe Timing Tests 82 Test Procedure 82                                                                                                                                                        |    |

|             | tHZ(DQ), DQ High Impedance Time From CK/CK# - Test Method of Implementation  Signals of Interest 85  Test Definition Notes from the Specification 85  PASS Condition 86                                          | 85 |

Measurement Algorithm

Test References 86

86

| tHZ(DQS), DQS High Impe                                                                                                       | dance Time From      | CK/CK# - Test Method of Implementation        | 8/ |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------|----|

| Signals of Interest 87 Test Definition Notes from PASS Condition 88 Measurement Algorithm Test References 88                  | the Specification    | 87                                            |    |

| tLZ(DQS), DQS Low-Imped                                                                                                       | ance Time from 0     | CK/CK# - Test Method of Implementation        | 89 |

| Signals of Interest 89 Test Definition Notes from PASS Condition 90 Measurement Algorithm Test References 90                  | the Specification    | 89                                            |    |

| :LZ(DQ), DQ Low-Impedan                                                                                                       | ce Time from CK/     | <b>CK# - Test Method of Implementation</b> 91 |    |

| Signals of Interest 91 Test Definition Notes from PASS Condition 92 Measurement Algorithm Test References 93                  | the Specification 92 | 92                                            |    |

| DQSQ, DQS-DQ Skew for                                                                                                         | DQS and Associa      | ted DQ Signals - Test Method of               |    |

| mplementation 94                                                                                                              |                      |                                               |    |

| Signals of Interest 94 Test Definition Notes from PASS Condition 94 Measurement Algorithm Test References 95                  | •                    | 94                                            |    |

| QH, DQ/DQS Output Hold                                                                                                        | Time From DQS -      | Test Method of Implementation 96              |    |

| Signals of Interest 96 Test Definition Notes from PASS Condition 96 Measurement Algorithm Test References 97                  | the Specification 96 | 96                                            |    |

| DQSS, DQS Latching Tran                                                                                                       | sition to Associat   | ed Clock Edge - Test Method of                |    |

| mplementation 98 Signals of Interest 98 Test Definition Notes from PASS Condition 98 Measurement Algorithm Test References 99 | the Specification 98 | 98                                            |    |

| tDQSH, DQS Input High Pulse Width - Test                                                                                                 | Method of Implementation 100             |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Signals of Interest 100 Test Definition Notes from the Specification PASS Condition 100 Measurement Algorithm 100 Test References 101    | 100                                      |

| tDQSL, DQS Input Low Pulse Width - Test I                                                                                                | Method of Implementation 102             |

| Signals of Interest 102 Test Definition Notes from the Specification PASS Condition 102 Measurement Algorithm 102 Test References 103    | 102                                      |

| tDSS, DQS Falling Edge to CK Setup Time -                                                                                                | <b>Test Method of Implementation</b> 104 |

| Signals of Interest 104 Test Definition Notes from the Specification PASS Condition 104 Measurement Algorithm 104 Test References 105    | 104                                      |

| tDSH, DQS Falling Edge Hold Time from CK                                                                                                 | - Test Method of Implementation 106      |

| Signals of Interest 106 Test Definition Notes from the Specification PASS Condition 106 Measurement Algorithm 106 Test References 107    | 106                                      |

| tWPST, Write Postamble - Test Method of I                                                                                                | mplementation 108                        |

| Signals of Interest 108  Test Definition Notes from the Specification PASS Condition 108  Measurement Algorithm 108  Test References 109 | 108                                      |

| tWPRE, Write Preamble - Test Method of In                                                                                                | nplementation 110                        |

| Signals of Interest 110  Test Definition Notes from the Specification PASS Condition 111  Measurement Algorithm 111                      | 110                                      |

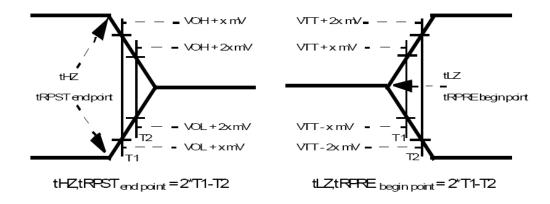

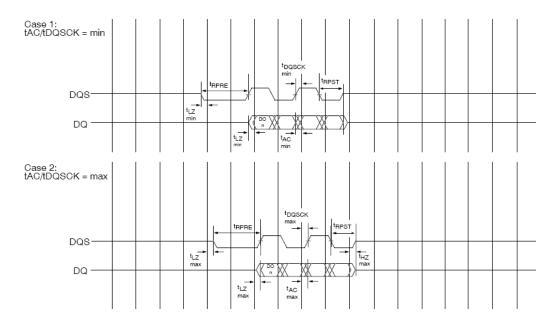

| tRPRE, Read Preamble - Test Method of Implementation 112                                                                                                                                                                         |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Signals of Interest 112 Test Definition Notes from the Specification 112 PASS Condition 112 Measurement Algorithm 113 Test References 113                                                                                        |    |

| tRPST, Read Postamble - Test Method of Implementation 114                                                                                                                                                                        |    |

| Signals of Interest 114 Chip Select Signal (CS as additional signal, which requires an additional channel) 114 Test Definition Notes from the Specification 114 PASS Condition 114 Measurement Algorithm 114 Test References 115 |    |

| 8 Clock Timing (CT) Tests                                                                                                                                                                                                        |    |

| Probing for Clock Timing Tests 118  Test Procedure 118                                                                                                                                                                           |    |

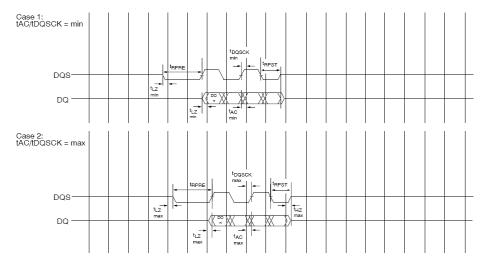

| tAC, DQ Output Access Time from CK/CK# - Test Method of Implementation 121                                                                                                                                                       |    |

| Signals of Interest 121 Test Definition Notes from the Specification 121 Pass Condition 122 Measurement Algorithm 122 Test References 123                                                                                        |    |

| tDQSCK, DQS Output Access Time from CK/CK #- Test Method of Implementation 1                                                                                                                                                     | 24 |

| Signals of Interest 125 Test Definition Notes from the Specification 126 PASS Condition 126 Measurement Algorithm 126 Test References 127                                                                                        |    |

| Average Clock Period - tCK(avg) - Test Method of Implementation 128                                                                                                                                                              |    |

| Signals of Interest 128 Test Definition Notes from the Specification 128 PASS Condition 128 Measurement Algorithm 129 Test References 129                                                                                        |    |

| Average High Pulse Width - tCH(avg) - Test Method of Implementation 130                                                                                                                                                          |    |

| Signals of Interest 130  Test Definition Notes from the Specification. 130  Pass Condition 130  Measurement Algorithm 130  Test References 130                                                                                   |    |

|    | Signals of Interest 131 Test Definition Notes from the Specification. 131 Pass Condition 131 Measurement Algorithm 131 Test References 131                                                                                      |     |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9  | Data Mask Timing (DMT) Tests                                                                                                                                                                                                    |     |

|    | Probing for Data Mask Timing Tests 134  Test Procedure 134                                                                                                                                                                      |     |

|    | tDS(base), DQ and DM Input Setup Time - Test Method of Implementation  Signals of Interest 137  Test Definition Notes from the Specification 137  PASS Condition 137  Measurement Algorithm 138  Test References 138            |     |

|    | tDH(base), DQ and DM Input Hold Time - Test Method of Implementation  Signals of Interest 139  Test Definition Notes from the Specification 139  PASS Condition 140  Measurement Algorithm 140  Test References 140             |     |

| 10 | Command and Address Timing (CAT) Tests                                                                                                                                                                                          |     |

|    | Probing for Command and Address Timing Tests 142  Test Procedure 143                                                                                                                                                            |     |

|    | tIS(base) - Address and Control Input Setup Time - Test Method of Implementation  Signals of Interest 145  Test Definition Notes from the Specification 145  PASS Condition 145  Measurement Algorithm 146  Test References 146 | 145 |

|    |                                                                                                                                                                                                                                 | 147 |

|    | Signals of Interest 147 Test Definition Notes from the Specification 147 PASS Condition 147 Measurement Algorithm 148 Test References 148                                                                                       |     |

| 11 | Advanced Debug Mode Clock Tests                                                                                                             |               |   |

|----|---------------------------------------------------------------------------------------------------------------------------------------------|---------------|---|

|    | Probing for Clock Tests 150  Test Procedure 150                                                                                             |               |   |

|    | Clock Period Jitter - tJIT(per) - Test Method of Implementation 15<br>Signals of Interest 154<br>Measurement Algorithm 154                  | 54            |   |

|    | Cycle to Cycle Period Jitter - tJIT(cc) - Test Method of Implementati<br>Signals of Interest 155<br>Measurement Algorithm 155               | <b>on</b> 155 | 5 |

|    | Cumulative Error - tERR(n per) - Test Method of Implementation  Signals of Interest 156  Measurement Algorithm 156                          | 56            |   |

|    | Half Period Jitter - tJIT(duty) - Test Method of Implementation 19<br>Signals of Interest 157<br>Measurement Algorithm 157                  | 57            |   |

| 12 | Advanced Debug Mode High-Low State Ringing Tests                                                                                            |               |   |

|    | Probing for Ad vanced Debug Mode High-Low State Ringing Tests  Test Procedure 160                                                           | 160           |   |

|    | High State Ringing Tests Method of Implementation 164 Signals of Interest 164 Measurement Algorithm 165                                     |               |   |

|    | Low State Ringing Tests Method of Implementation 166 Signals of Interest 166 Measurement Algorithm 167                                      |               |   |

| 13 | Calibrating the Infiniium Oscilloscope and Probe                                                                                            |               |   |

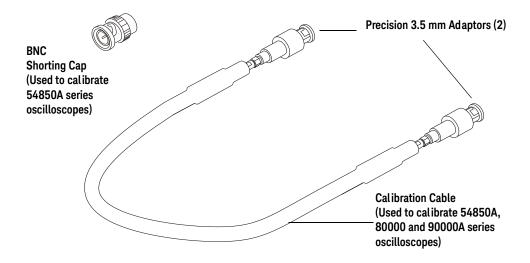

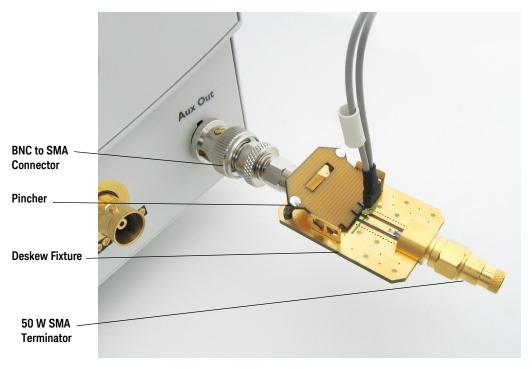

|    | Required Equipment for Oscilloscope Calibration 170                                                                                         |               |   |

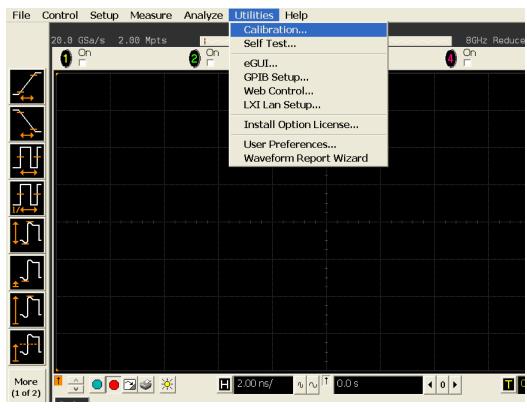

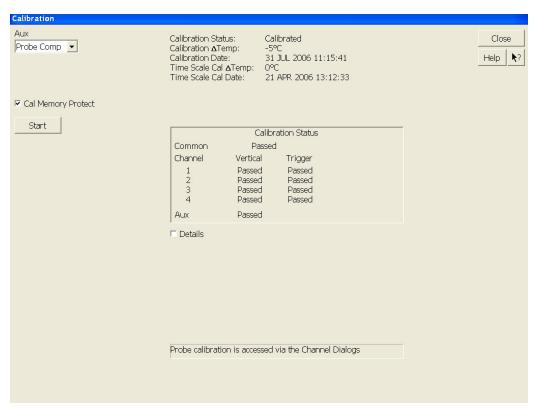

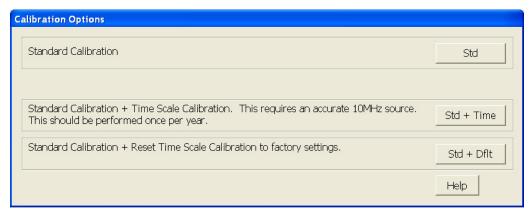

|    | Internal Calibration 171                                                                                                                    |               |   |

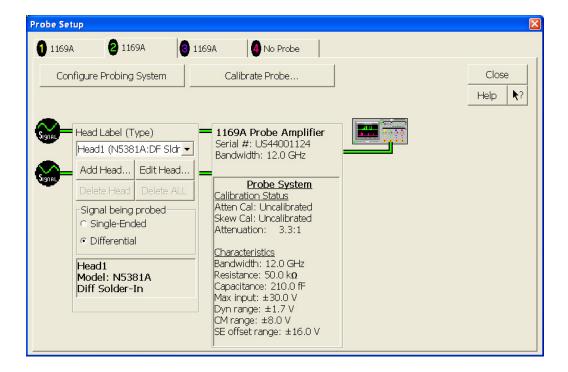

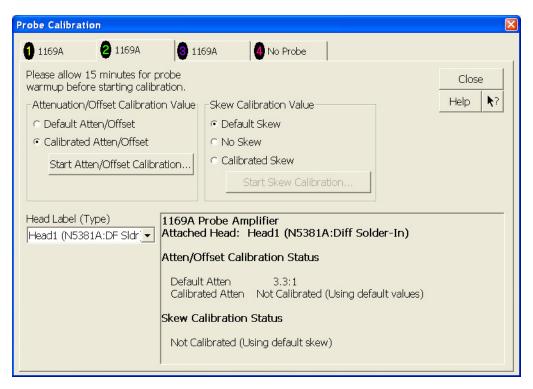

|    | Required Equipment for Probe Calibration 174                                                                                                |               |   |

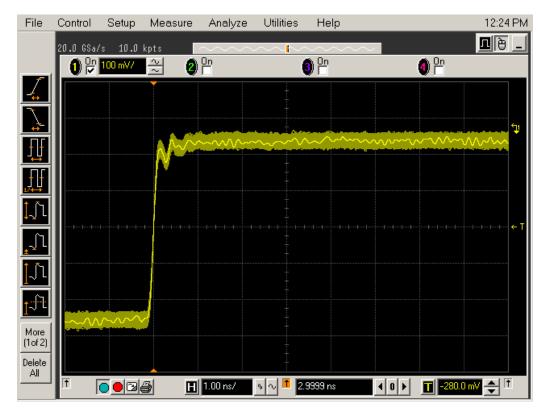

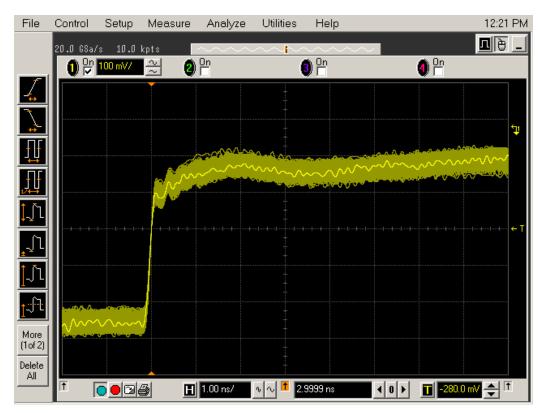

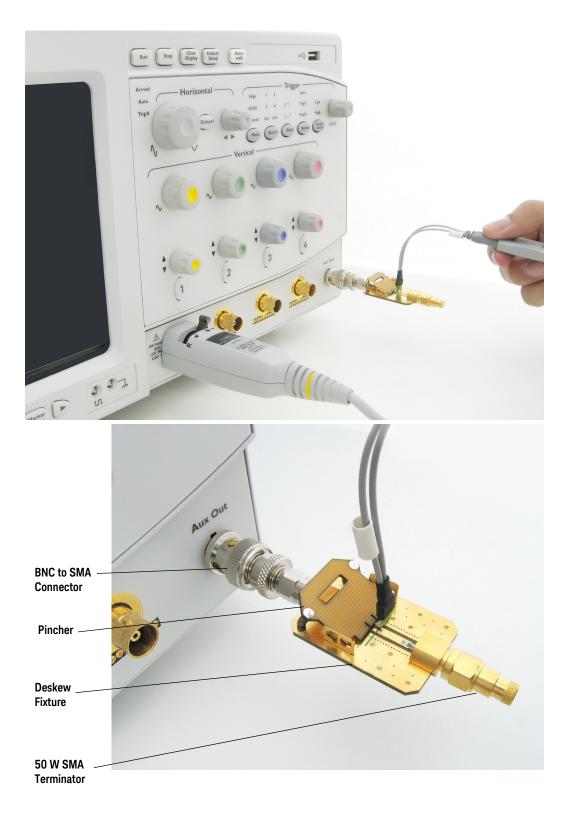

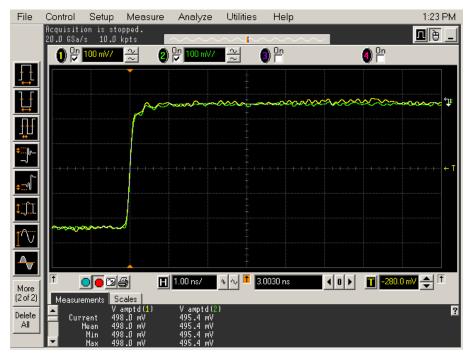

|    | Probe Calibration 175  Connecting the Probe for Calibration 175  Verifying the Connection 177  Running the Probe Calibration and Deskew 179 |               |   |

|    | Verifying the Probe Calibration 182                                                                                                         |               |   |

# 14 InfiniiMax Probing

# 15 Common Error Messages

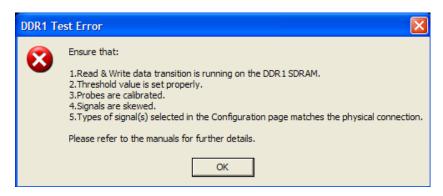

**Required Triggering Condition Not Met** 188

**Software License Error** 190

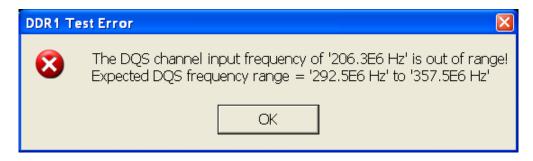

Frequency Out of Range Error 191

Missing Signal Error 192

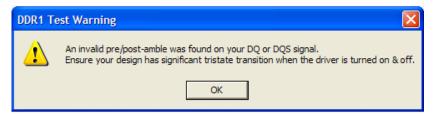

**Invalid Pre/PostAmble Signal Error** 193

Index

Contents

# Keysight U7233A DDR1 Compliance Test Application Compliance Testing Methods of Implementation

# Installing the DDR1 Compliance Test Application

Installing the Software / 22

Installing the License Key / 23

If you purchased the U7233A DDR1 Compliance Test Application separately, you need to install the software and license key.

### 1

# Installing the Software

- 1 Make sure you have version 05.30 or higher of the Infiniium oscilloscope software or baseline software revision 1.0 by choosing Help>About Infiniium... from the main menu.

- 2 To obtain the DDR1 Compliance Test Application, go to Keysight website: http://www.keysight.com/find/U7233A.

- 3 The link for DDR1 Compliance Test Application will appear. Double-click on it and follow the instructions to download and install the application software.

## Installing the License Key

- 1 Request a license code from Keysight by following the instructions on the Entitlement Certificate. You will need the oscilloscope's "Option ID Number", which you can find in the Help>About Infiniium... dialog box.

- 2 After you receive your license code from Keysight, choose Utilities>Install Option License....

- 3 In the Install Option License dialog, enter your license code and click Install License.

- 4 Click OK in the dialog that tells you to restart the Infiniium oscilloscope application software to complete the license installation.

- 5 Click Close to close the Install Option License dialog.

- 6 Choose File>Exit.

- 7 Restart the Infiniium oscilloscope application software to complete the license installation.

1 Installing the DDR1 Compliance Test Application

# Keysight U7233A DDR1 Compliance Test Application Compliance Testing Methods of Implementation

# 2 Preparing to Take Measurements

Calibrating the Oscilloscope / 26 Starting the DDR1 Compliance Test Application / 27

Before running the DDR1 automated tests, you should calibrate the oscilloscope and probe. No test fixture is required for application. After the oscilloscope and probe have been calibrated, you are ready to start the DDR1 Compliance Test Application and perform the measurements.

## Calibrating the Oscilloscope

If you haven't already calibrated the oscilloscope and probe, see Chapter 13, "Calibrating the Infiniium Oscilloscope and Probe.

NOTE

If the ambient temperature changes more than 5 degrees Celsius from the calibration temperature, internal calibration should be performed again. The delta between the calibration temperature and the present operating temperature is shown in the Utilities>Calibration menu.

NOTE

If you switch cables between channels or other oscilloscopes, it is necessary to perform cable and probe calibration again. Keysight recommends that, once calibration is performed, you label the cables with the channel on which they were calibrated.

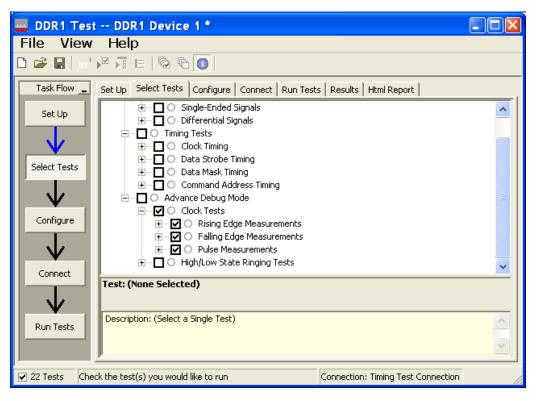

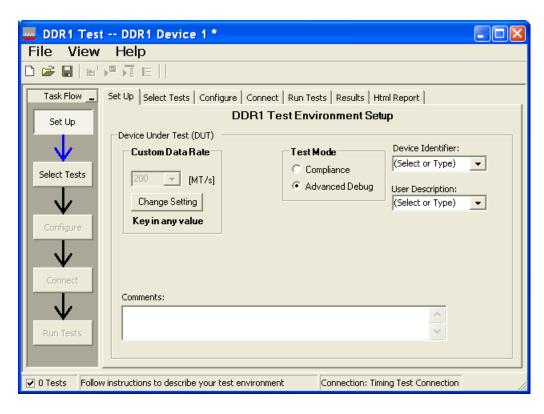

### Starting the DDR1 Compliance Test Application

- 1 Ensure that the RAM reliability test software is running in the computer system where the Device Under Test (DUT) is attached. This software performs tests to all unused RAM in the system by producing a repetitive burst of read-write data signals to the DDR memory.

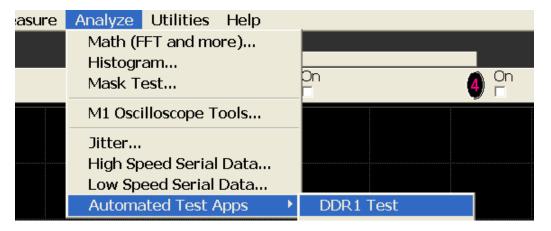

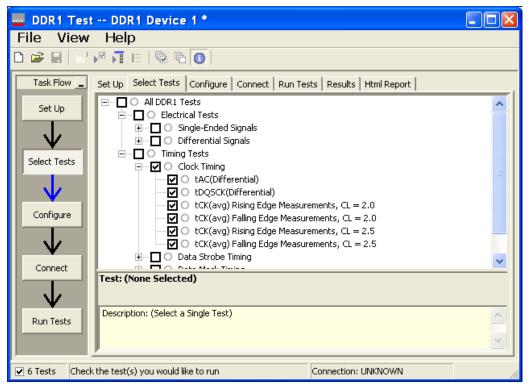

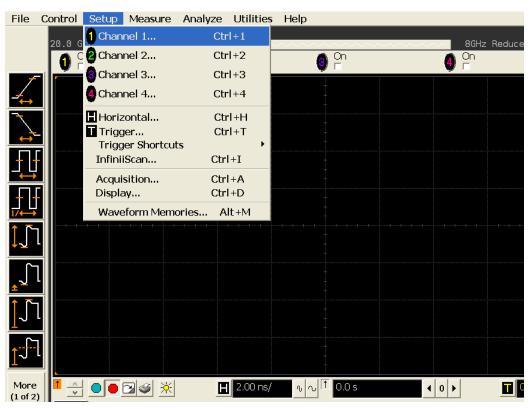

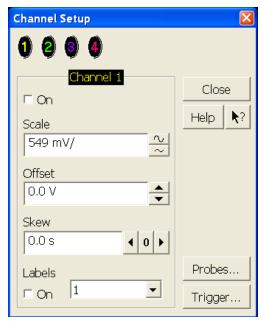

- To start the DDR1 Compliance Test Application: From the Infiniium oscilloscope's main menu, choose Analyze>Automated Test Apps>DDR1 Test.

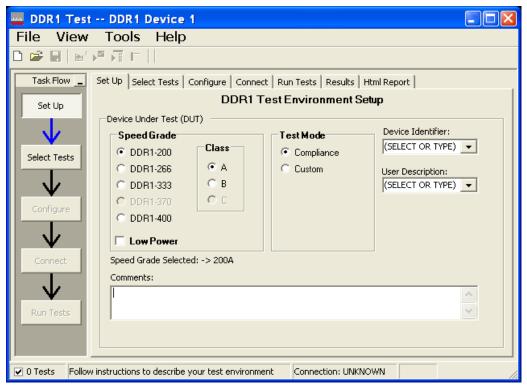

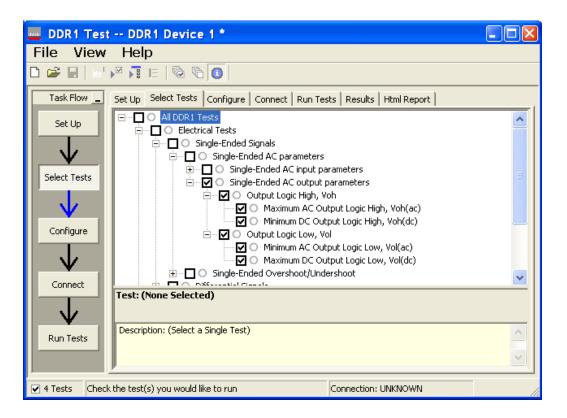

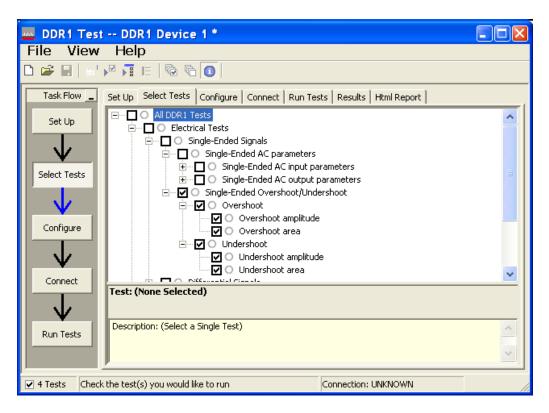

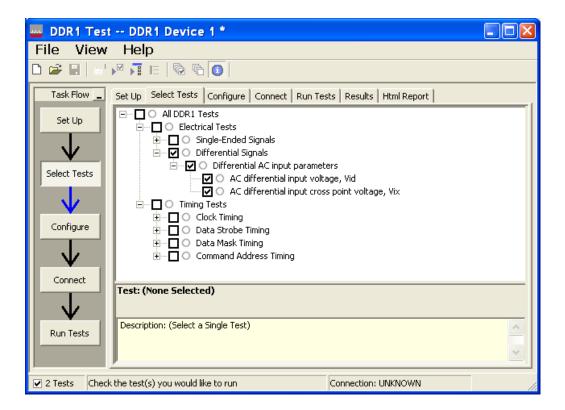

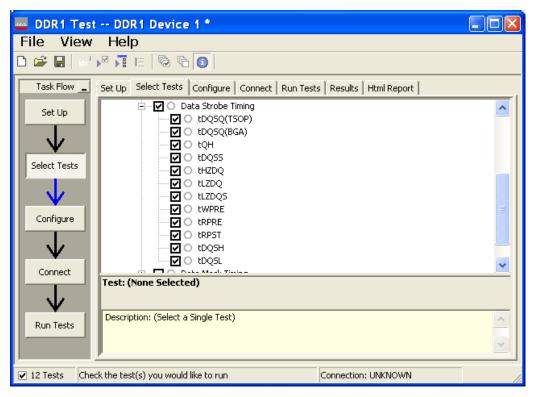

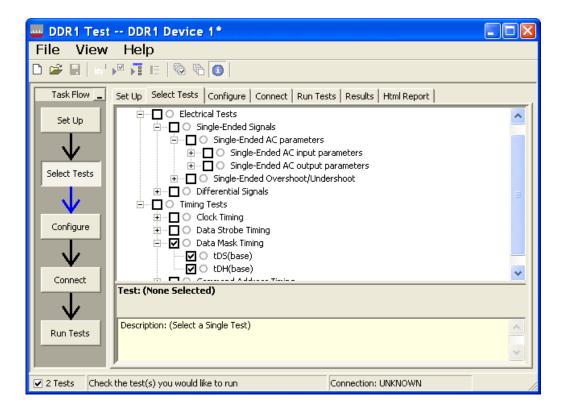

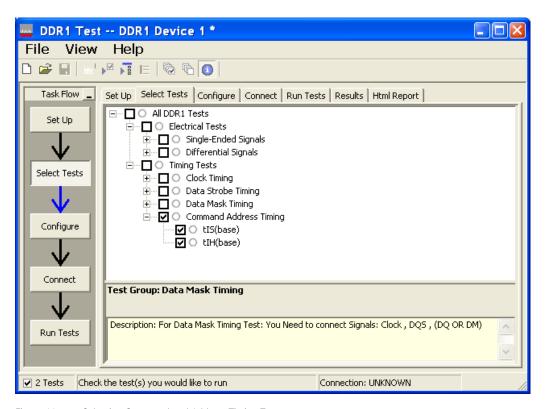

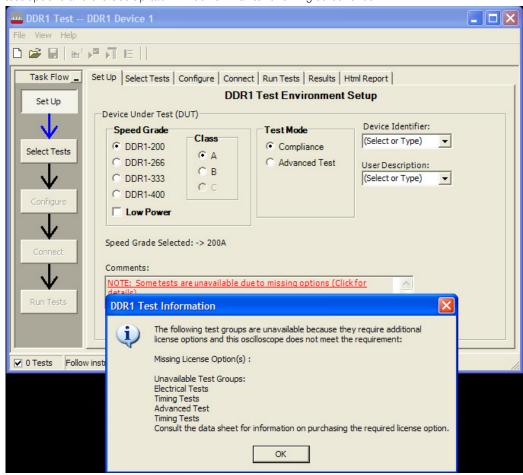

Figure 1 The DDR1 Compliance Test Application

# NOTE

If DDR1 Test does not appear in the Automated Test Apps menu, the DDR1 Compliance Test Application has not been installed (see Chapter 1, "Installing the DDR1 Compliance Test Application).

Figure 1 shows the DDR1 Compliance Test Application main window. The task flow pane, and the tabs in the main pane, show the steps you take in running the automated tests:

| Tab          | Description                                                                                                                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set Up       | Lets you identify and setup the test environment, including information about the device under test.                                                                                                                                                                       |

| Select Tests | Lets you select the tests you want to run. The tests are organized hierarchically so you can select all tests in a group. After tests are run, status indicators show which tests have passed, failed, or not been run, and there are indicators for the test groups.      |

| Configure    | Lets you configure test parameters (like memory depth). This information appears in the HTML report.                                                                                                                                                                       |

| Connect      | Shows you how to connect the oscilloscope to the device under test for the tests to be run.                                                                                                                                                                                |

| Run Tests    | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing. |

| Results      | Contains more detailed information about the tests that have been run. You can change the thresholds at which marginal or critical warnings appear.                                                                                                                        |

| HTML Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                        |

## NOTE

When you close the DDR1 application, each channel's probe is configured as single-ended or differential depending on the last DDR1 test that was run.

### Online Help Topics

For information on using the DDR1 Compliance Test Application, see its online help (which you can access by choosing Help>Contents... from the application's main menu).

The DDR1 Compliance Test Application's online help describes:

- · Starting the DDR1 Automated Test Application.

- · To view or minimize the task flow pane.

- · To view or hide the toolbar.

- · Creating or opening a test project.

- · Setting up DDR1 test environment.

- · Selecting tests.

- · Configuring selected tests.

- · Connecting the oscilloscope to the Device Under Test (DUT).

- · Running tests.

- · Viewing test results.

- · To show reference images and flash mask hits.

- · To change margin thresholds.

- Viewing/printing the HTML test report.

- · Understanding the HTML report.

- Saving test projects.

2 Preparing to Take Measurements

# Keysight U7233A DDR1 Compliance Test Application Compliance Testing Methods of Implementation

# 3 Single-Ended Signals AC Input Parameters Tests

Probing for Single-Ended Signals AC Input Parameters Tests / 32 SlewR Test Method of Implementation / 35 SlewF Test Method of Implementation / 38 VIH(AC) Test Method of Implementation / 41 VIH(DC) Test Method of Implementation / 44 VIL(AC) Test Method of Implementation / 47 VIL(DC) Test Method of Implementation / 50

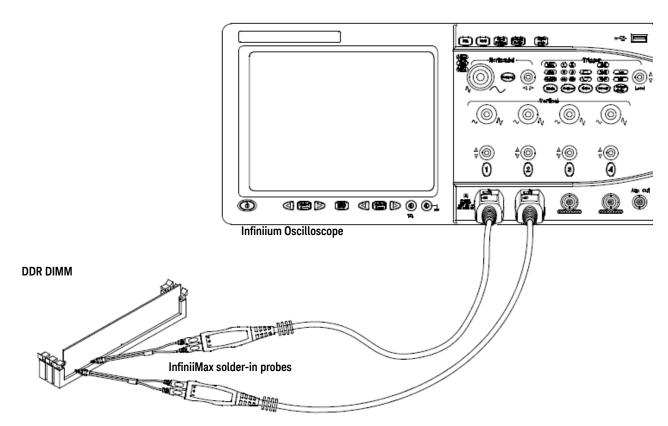

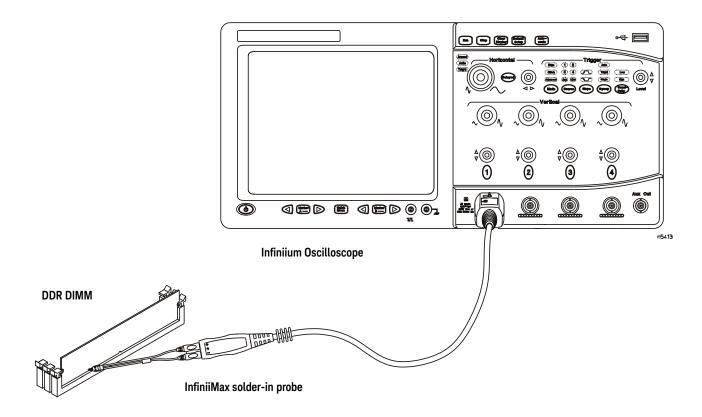

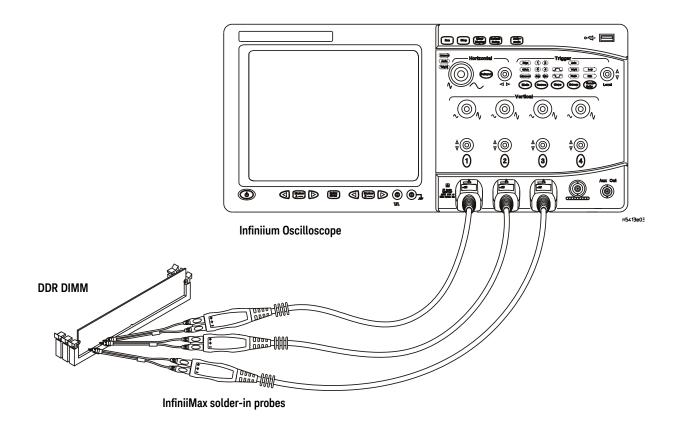

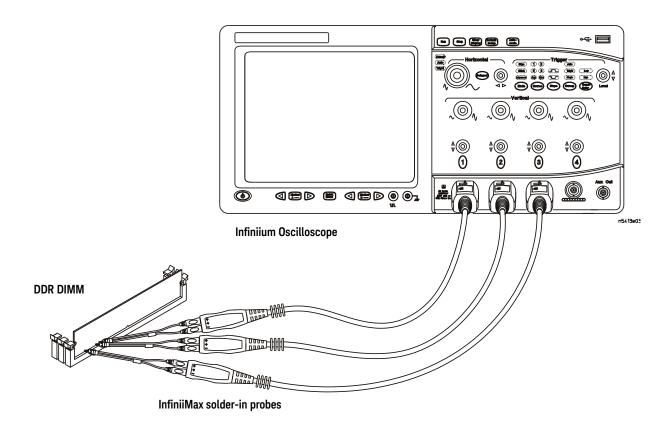

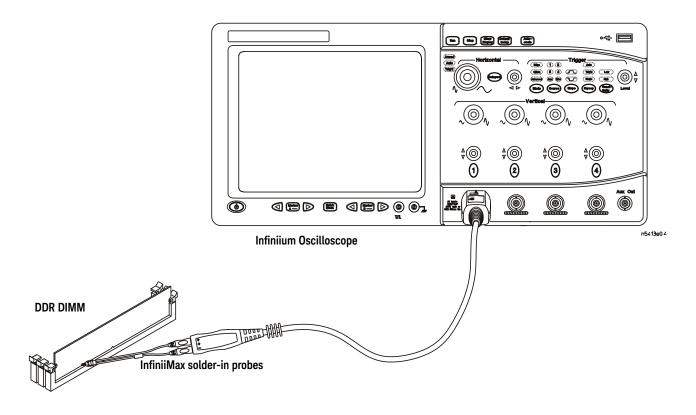

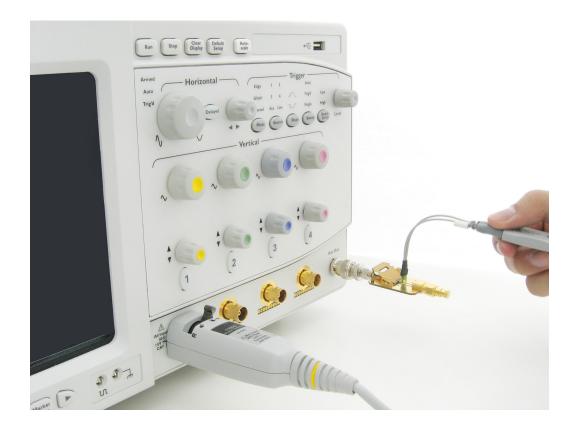

This section provides the Methods of Implementation (MOIs) for Single-Ended Signals AC Input tests using an Keysight 54850A, 8000, 80000 or 90000A series Infiniium oscilloscope, recommended InfiniiMax 116xA or 113xA probe amplifiers, E2677A differential solder-in probe head and the DDR1 Compliance Test Application.

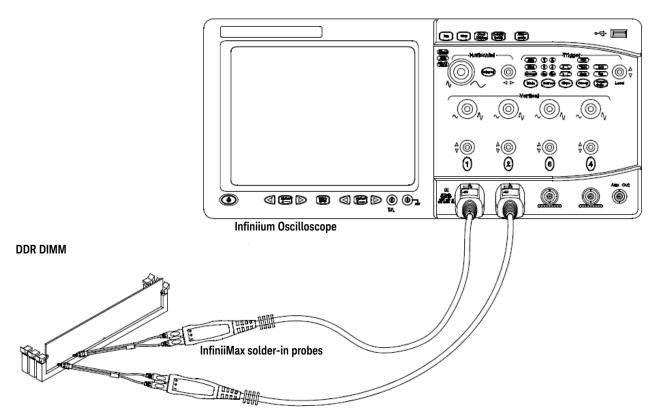

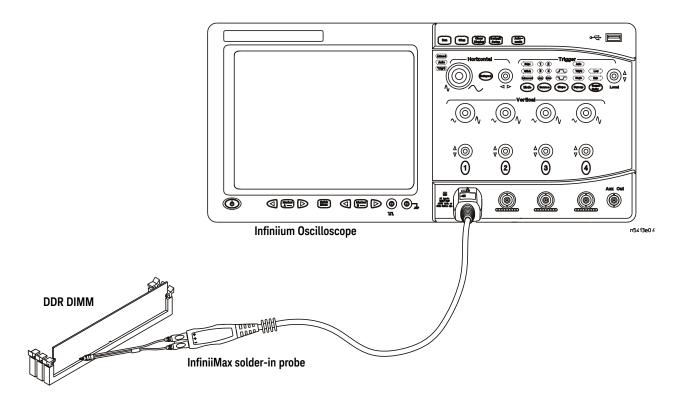

## Probing for Single-Ended Signals AC Input Parameters Tests

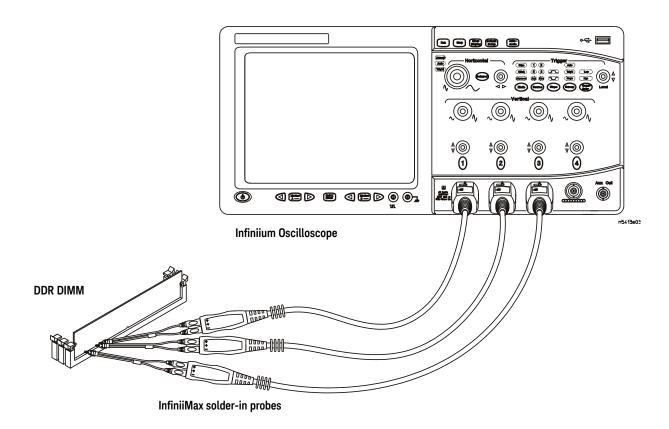

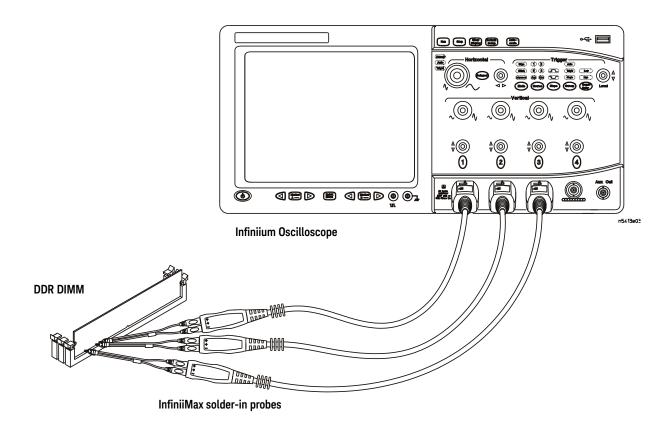

When performing the Single-Ended Signals AC Input Parameters tests, the DDR1 Compliance Test Application will prompt you to make the proper connections. The connection for the Single-Ended Signals AC Input Parameters tests may look similar to the following diagram. Refer to the Connection tab in DDR1 Compliance Test Application for the exact number of probe connections.

Figure 2 Probing for Single-Ended Signals AC Input Parameters Tests with Two Probes

You can use any of the oscilloscope channels as Pin Under Test (PUT) source channel. You can identify the channels used for each signal in the Configuration tab of the DDR1 Compliance Test Application. (The channels shown in Figure 2 are just examples).

For more information on the probe amplifiers and differential probe heads, see Chapter 14, "InfiniiMax Probing," starting on page 185.

### Test Procedure

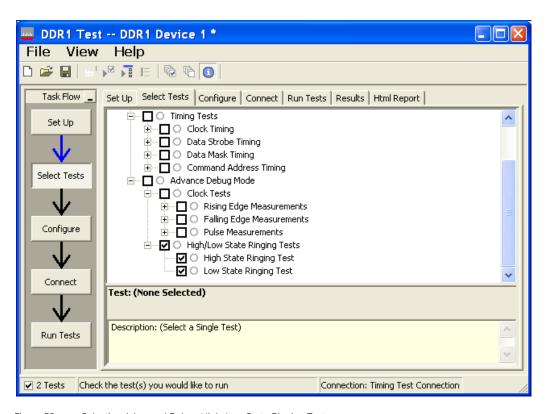

- 1 Start the automated test application as described in "Starting the DDR1 Compliance Test Application" on page 27.

- 2 Ensure that the RAM reliability test software is running on the computer system where the DDR Device Under Test (DUT) is attached. This software will perform a test on all unused RAM on the system by producing a repetitive burst of read-write data signals to the DDR memory.

- 3 Connect the differential solder-in probe head to the PUTs on the DDR DIMM.

- 4 Connect the oscilloscope probes to any channels of the oscilloscope.

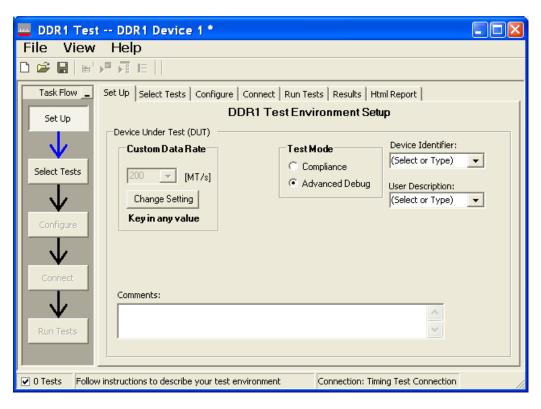

- 5 In the DDR1 Test Application, click the Set Up tab.

- 6 Select the Speed Grade options. For the Single-Ended Signals AC Input Parameters Tests, you can select any speed grade within the selection: DDR1-200, DDR1-266, DDR1-333, DDR1-400.

- 7 Type in or select the Device Identifier as well as User Description from the drop-down list. Enter your comments in the Comments text box.

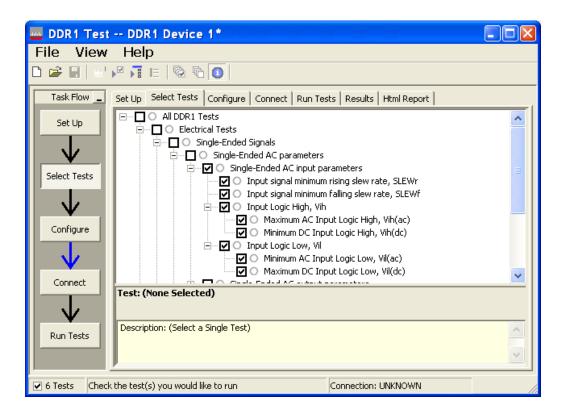

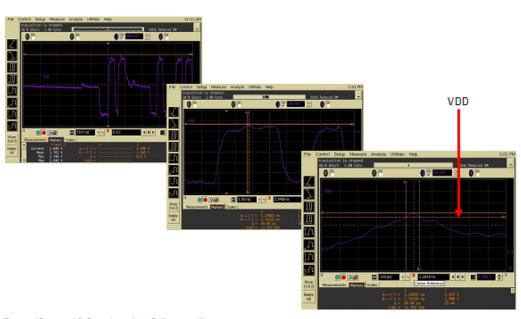

- 8 Click the Select Tests tab and check the tests you want to run. Check the parent node or group to check all the available tests within the group.

Figure 3 Selecting Single-Ended Signals AC Input Parameters Tests

3

9 Follow the DDR1 Test Application's task flow to set up the configuration options (see Table 2), run the tests and view the tests results.

Table 2 Test Configuration Options

| Configuration Option                   | Description                                                                                                                                                                                                                                                                      |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stop on error                          | Enabling this error message will allow error message to prompt whenever criteria is not met. Disabling this option will allow the system to bypass all the error messages that could occur and continue to the next test. This option is suitable for long hours multiple trial. |

| Signal Threshold setting by percentage | This option allow user to define the Upper and Lower threshold of the signal by percentage.                                                                                                                                                                                      |

| VDD                                    | Input supply voltage value.                                                                                                                                                                                                                                                      |

| VDDQ                                   | Input supply voltage for data output.                                                                                                                                                                                                                                            |

| Vref                                   | Input reference voltage value.                                                                                                                                                                                                                                                   |

| Vih(DC)                                | Input voltage high value (direct current).                                                                                                                                                                                                                                       |

| Vih(AC)                                | Input voltage high value (alternating current).                                                                                                                                                                                                                                  |

| Vil(DC)                                | Input voltage low value (direct current).                                                                                                                                                                                                                                        |

| Vil(AC)                                | Input voltage low value (alternating current).                                                                                                                                                                                                                                   |

| InfiniiScan Limits                     |                                                                                                                                                                                                                                                                                  |

| Read Cycle                             |                                                                                                                                                                                                                                                                                  |

| IScan_UL_READ                          | Identifies the upper limit for Setup Time measurement used in the InfiniiScan Measurement Mode (READ cycle)                                                                                                                                                                      |

| IScan_LL_READ                          | Identifies the lower limit for Setup Time measurement used in the InfiniiScan Measurement Mode (READ cycle)                                                                                                                                                                      |

| Write Cycle                            |                                                                                                                                                                                                                                                                                  |

| IScan_UL_WRITE                         | Identifies the upper limit for Setup Time measurement used in the InfiniiScan Measurement Mode (WRITE cycle)                                                                                                                                                                     |

| IScan_LL_WRITE                         | Identifies the upper limit for Setup Time measurement used in the InfiniiScan Measurement Mode (WRITE cycle)                                                                                                                                                                     |

| Single-Ended Signals                   |                                                                                                                                                                                                                                                                                  |

| Single-Ended AC<br>Parameters          |                                                                                                                                                                                                                                                                                  |

| Pin Under Test, PUT                    | Identifies the Pin Under Test for Single-Ended AC parameters.                                                                                                                                                                                                                    |

| PUT Source                             | Identifies the source of the PUT to be analyzed for Single-Ended AC tests.                                                                                                                                                                                                       |

| Supporting Pin                         | Identifies the required supporting pin for Single-Ended AC parameters.                                                                                                                                                                                                           |

| Supporting Pin Source                  | Identifies the source of the supporting pin for Single-Ended AC Tests.                                                                                                                                                                                                           |

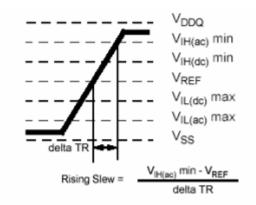

# Slew<sub>R</sub> Test Method of Implementation

$Slew_R$  - Input Signal Minimum Slew Rate (Rising). The purpose of this test is to verify that the rising slew rate value of the test signal is greater than or equal to the conformance limit of the input SLEW value specified in the *JEDEC Standard JESD79E*.

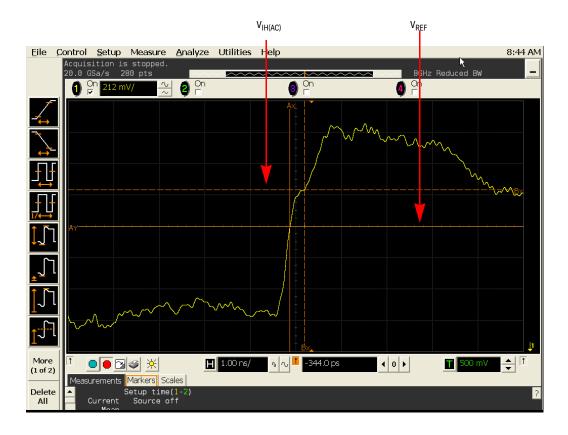

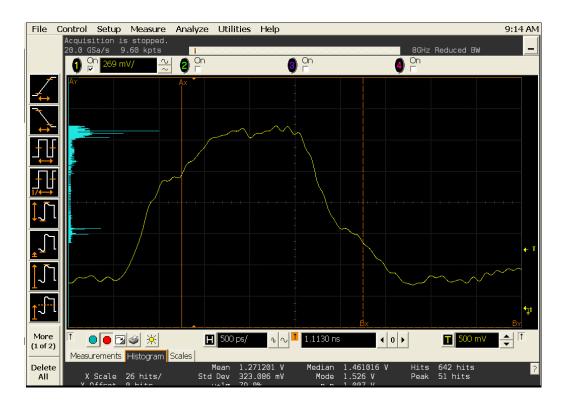

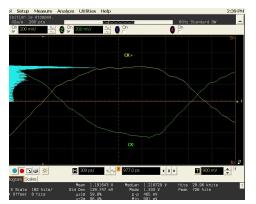

Figure 4 Slew<sub>R</sub>

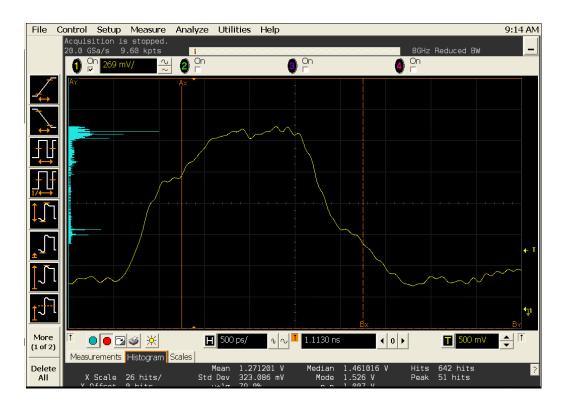

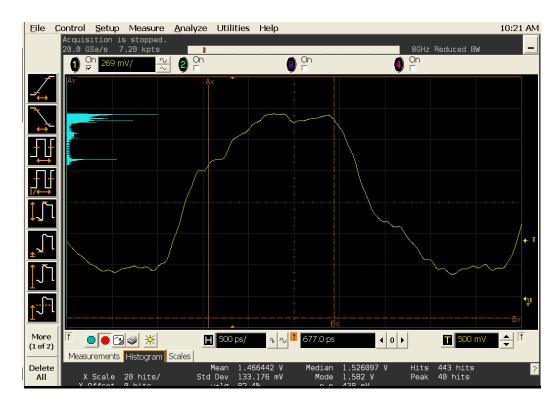

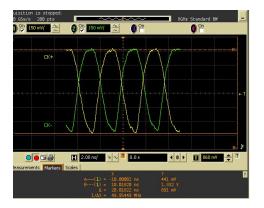

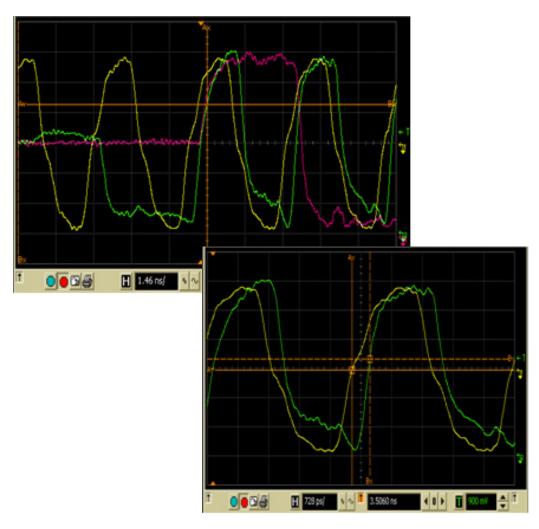

Figure 5 Slew<sub>R</sub> in Infiniium oscilloscope

### Signals of Interest

Based on the test definition (Write cycle only):

- Data Signal

- · Data Strobe Signal OR

- · Address Signal OR

- · Control Signal OR

- · Data Mask Control Signals

Signals required to perform the test on the oscilloscope:

- · Data Signal (DQ as Pin Under Test Signal)\*

- Data Strobe Signal (DQS as Supporting Signal)

- Clock Signal CK is required to perform pre-test to verify the DUT speed against user's speed grade selection

- \* Pin Under Test signal can be either one of the signals under the test definition.

Test Definition Notes from the Specification

Table 3 Input Slew Rate for DQ, DQS and DM

| AC Characteristics - Parameter                                                   | Symbol | DDR 400 |     | DDR 333 |     | DDR 266 |     | DDR 200 |     | Units | Notes |

|----------------------------------------------------------------------------------|--------|---------|-----|---------|-----|---------|-----|---------|-----|-------|-------|

|                                                                                  |        | Min     | Max | Min     | Max | Min     | Max | Min     | Max | _     |       |

| DQ/DM/DQS input slew rate measured between VIH(DC), VIL(DC) and VIL(DC), VIH(DC) | DCSlew | 0.5     | 4.0 | 0.5     | 4.0 | 0.5     | 4.0 | 0.5     | 4.0 | V/ns  | a, m  |

NOTE a and m: Please refer to the JEDEC Standard JESD79E.

### **PASS Condition**

### $\geq$ SLEW<sub>R</sub>

The calculated Rising Slew value for the test signal should be greater than or equal to the SLEW value.

### Measurement Algorithm

- 1 Calculate the initial time scale value based on the selected DDR1 speed grade.

- 2 Pre-condition the scope settings. Verify the actual DUT speed against the user speed selection at the Setup page.

- 3 Calculate the number of sampling points according to the time scale value.

- 4 Obtain sample or acquire signal data and perform signal conditioning to maximize the screen resolution (vertical scale adjustment).

- 5 Perform signal checking on all the signals in-use in the measurement to ensure that it can be triggered during the test. This includes Vp-p, Vmin, Vmax and Vmid of each signal.

- 6 Perform signal skew checking on the DQ-DQS to ensure that it can be triggered during the Read/Write separation later.

- 7 Setup the required scope settings and histogram function settings.

- 8 Verify that  $V_{REF}$  and  $V_{IH(AC)}$  points can be found on the oscilloscope screen.

- 9 Calculate the delta TR.

- 10 Calculate Rising Slew.

$$RisingSlew = \frac{V_{IH(ac)}min - V_{REF}}{\Delta TR}$$

11 Compare test results against the compliance test limit.

# Test References

See Table 13 - Input Slew Rate for DQ, DQS, and DM, in the JEDEC Standard JESD79E.

#### 3

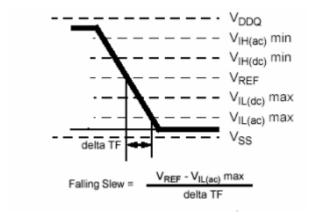

# Slew<sub>F</sub> Test Method of Implementation

$Slew_F$  - Input Signal Minimum Slew Rate (Falling). The purpose of this test is to verify that the falling slew rate value of the test signal is greater than or equal to the conformance limit of the input SLEW value specified in the *JEDEC Standard JESD79E*.

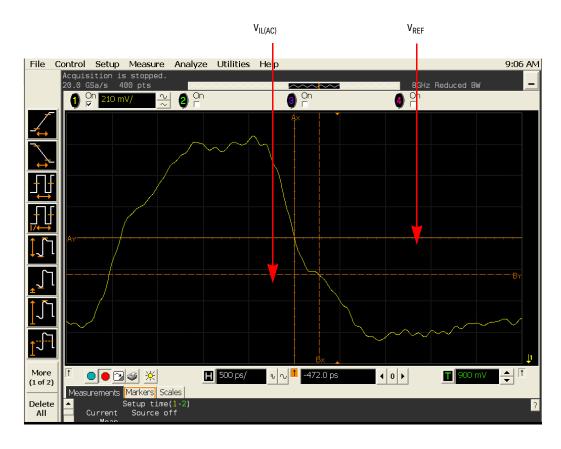

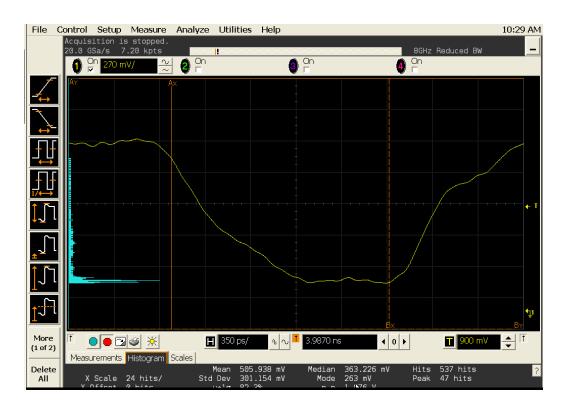

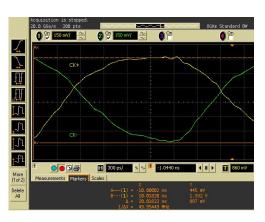

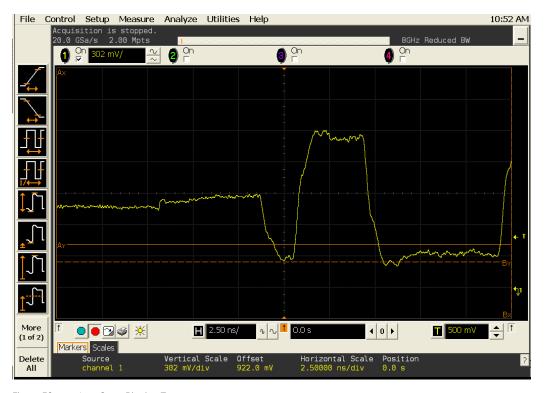

Figure 6 Slew<sub>F</sub>

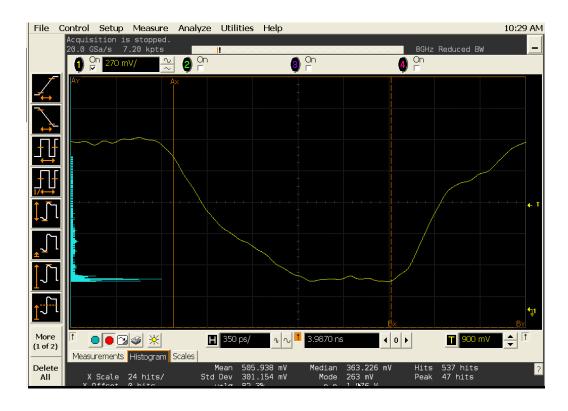

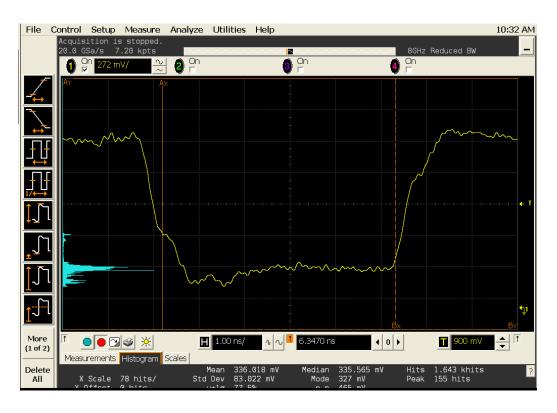

Figure 7 Slew<sub>F</sub> in Infiniium oscilloscope

# Signals of Interest

Based on the test definition (Write cycle only):

- · Data Signal

- · Data Strobe Signal OR

- · Address Signal OR

- · Control Signal OR

- · Data Mask Control Signals

Signals required to perform the test on the oscilloscope:

- · Data Signal (DQ as Pin Under Test Signal)\*

- Data Strobe Signal (DQS as Supporting Signal)

- Clock Signal CK is required to perform pre-test to verify the DUT speed against user's speed grade selection

- \* Pin Under Test signal can be either one of the signals under the test definition.

Test Definition Notes from the Specification

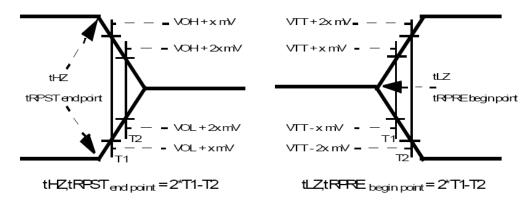

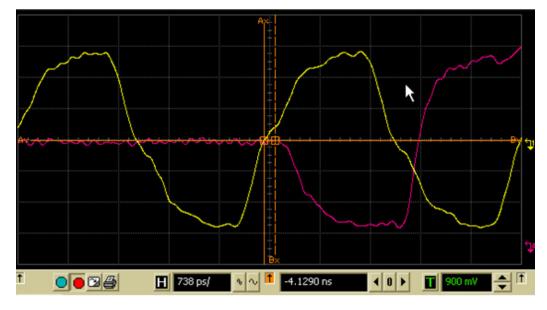

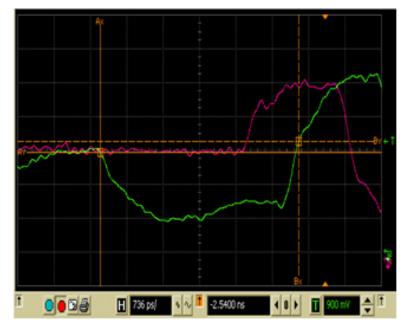

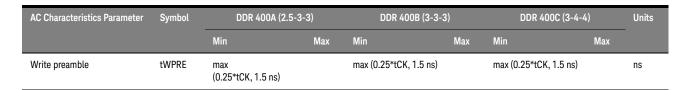

Table 4 Input Slew Rate for DQ, DQS, and DM